- 您现在的位置:买卖IC网 > Sheet目录3871 > PIC18F4682T-I/ML (Microchip Technology)IC PIC MCU FLASH 40KX16 44QFN

PIC18F46J50 FAMILY

DS39931D-page 140

2011 Microchip Technology Inc.

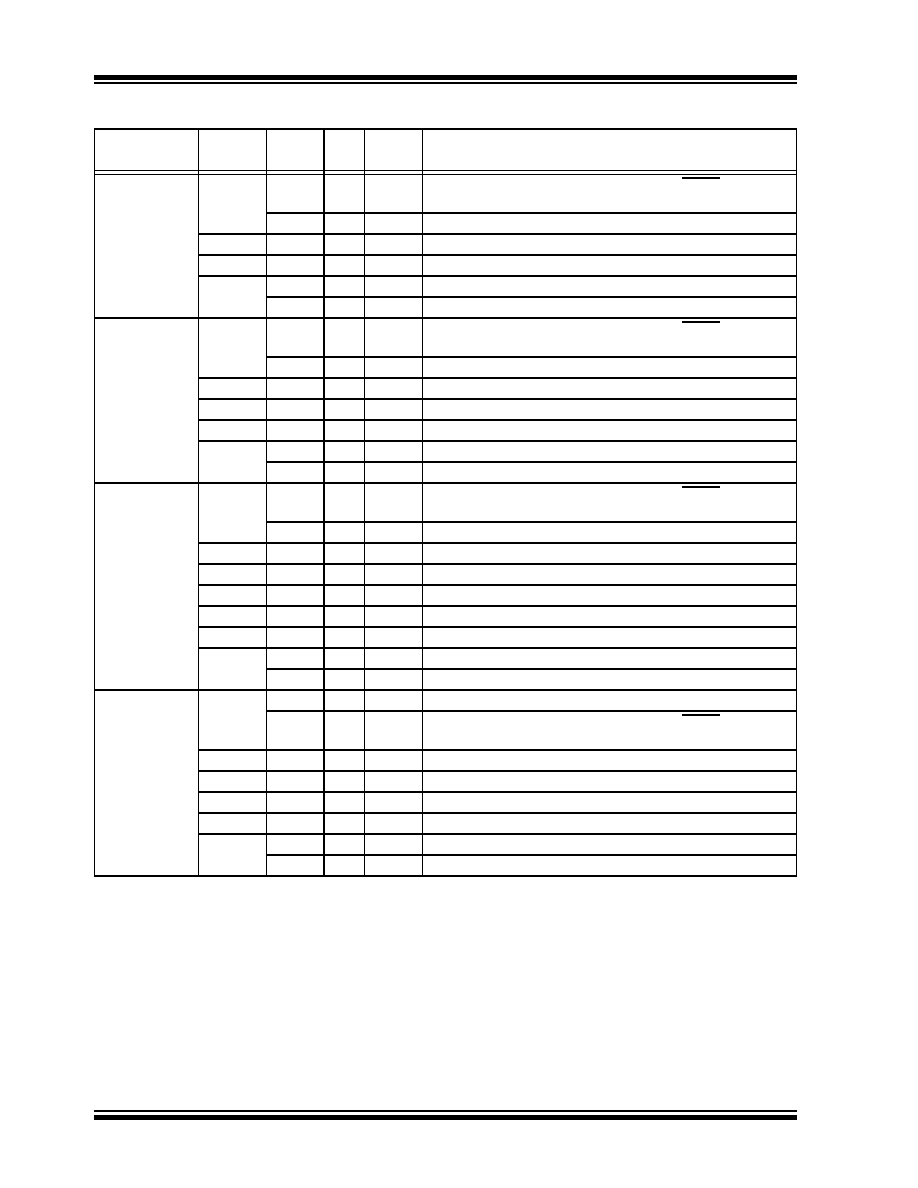

TABLE 10-5:

PORTB I/O SUMMARY

Pin

Function

TRIS

Setting

I/O

Type

Description

RB0/AN12/

INT0/RP3

RB0

1

I

TTL

PORTB<0> data input; weak pull-up when RBPU bit is

cleared. Disabled when analog input is enabled.(1)

0

O

DIG

LATB<0> data output; not affected by analog input.

AN12

1

I

ANA

A/D Input Channel 12.(1)

INT0

1

I

ST

External Interrupt 0 input.

RP3

1

I

ST

Remappable Peripheral Pin 3 input.

0

O

DIG

Remappable Peripheral Pin 3 output.

RB1/AN10/

PMBE/RTCC/

RP4

RB1

1

I

TTL

PORTB<1> data input; weak pull-up when RBPU bit is

cleared. Disabled when analog input is enabled.(1)

0

O

DIG

LATB<1> data output; not affected by analog input.

AN10

1

I

ANA

A/D Input Channel 10.(1)

PMBE(3)

0

O

DIG

Parallel Master Port byte enable output.

RTCC

0

O

DIG

Real-Time Clock Calender output.

RP4

1

I

ST

Remappable Peripheral Pin 4 input.

0

O

DIG

Remappable Peripheral Pin 4 output.

RB2/AN8/

CTED1/PMA3/

VMO/REFO/

RP5

RB2

1

I

TTL

PORTB<2> data input; weak pull-up when RBPU bit is

cleared. Disabled when analog input is enabled.(1)

0

O

DIG

LATB<2> data output; not affected by analog input.

AN8

1

I

ANA

A/D Input Channel 8.(1)

CTED1

1

I

ST

CTMU Edge 1 input.

PMA3(3)

0

O

DIG

Parallel Master Port address.

VMO

0

O

DIG

External USB transceiver D – data output.

REFO

0

O

DIG

Reference output clock.

RP5

1

I

ST

Remappable Peripheral Pin 5 input.

0

O

DIG

Remappable Peripheral Pin 5 output.

RB3/AN9/

CTED2/PMA2/

VPO/RP6

RB3

0

O

DIG

LATB<3> data output; not affected by analog input.

1

I

TTL

PORTB<3> data input; weak pull-up when RBPU bit is

cleared. Disabled when analog input is enabled.(1)

AN9

1

I

ANA

A/D Input Channel 9.(1)

CTED2

1

I

ST

CTMU Edge 2 input.

PMA2(3)

0

O

DIG

Parallel Master Port address.

VPO

0

I

DIG

External USB transceiver D+ data output.

RP6

1

I

ST

Remappable Peripheral Pin 6 input.

0

O

DIG

Remappable Peripheral Pin 6 output.

Legend:

DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level

input/output; x = Don’t care (TRIS bit does not affect port direction or is overridden for this option)

Note 1:

Pins are configured as analog inputs by default on POR. Using these pins for digital inputs requires setting

the appropriate bits in the ANCONx register first.

2:

All other pin functions are disabled when ICSP or MPLAB ICD are enabled.

3:

This functionality is only available on 44-pin devices.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24HJ128GP306T-I/PT

IC PIC MCU FLASH 128KB 64TQFP

PIC24FJ96GA008T-I/PT

IC PIC MCU FLASH 96KB 80TQFP

PIC24FJ64GA010T-I/PT

IC PIC MCU FLASH 64KB 100TQFP

PIC24FJ64GA008T-I/PT

IC PIC MCU FLASH 64KB 80TQFP

PIC18LF4450T-I/PT

IC PIC MCU FLASH 8KX16 44TQFP

PIC18LF2450T-I/ML

IC PIC MCU FLASH 8KX16 28QFN

PIC16F1937-I/ML

IC PIC MCU FLASH 512KX14 44-QFN

PIC18F25K20-E/ML

IC PIC MCU FLASH 16KX16 28-QFN

相关代理商/技术参数

PIC18F4682T-I/PT

功能描述:8位微控制器 -MCU 80KB FL 3328bytes RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4685-E/ML

功能描述:8位微控制器 -MCU 96KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4685-E/P

功能描述:8位微控制器 -MCU 96KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4685-E/PT

功能描述:8位微控制器 -MCU 96KB FL 3328bytes RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4685-I/ML

功能描述:8位微控制器 -MCU 96KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4685-I/ML

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 40MHZ QFN-44 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 40MHZ, QFN-44

PIC18F4685-I/P

功能描述:8位微控制器 -MCU 96KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4685-I/P

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC